磁気コアメモリは、Mn-Mg系フェライトコアの持つ矩形ヒステリシス磁化特性を利用した記憶装置で、

コアの磁化方向をそれぞれ 0 と 1 に対応させることでコア1個あたり1ビットの記憶ができます。

コアのサイズは集積度を上げるために非常に小さく、内径 0.5mm くらいのものまであります。

まず、コアに書き込み線と読み出し線と呼ばれる2つの導線を通しておきます。

書き込みをするときは、書き込み線にあるしきい値以上の電流を流すと、コアが磁化されます。この時の磁化の方向を「 1 」とします。

読み出しをするときは、書き込み線に書き込み時とは逆向きの電流を流し、読み出し線にパルス状の電圧が観測されるかどうかを検出します。

もし、「 1 」が書き込まれていたら、コアの磁束が変化するためパルスが発生しますが、「 0 」が書き込まれていたなら磁束は変化せず、パルスは発生しません。

読み出しとは、コアに「 0 」を書き込むことと同じなので、情報を読み出すと記録されたデータは失われます。このようなメモリの特性を破壊読み出しといいます。

読み出しと書込みはどのような場合でもセットで行われるのが普通で、読み出したデータを一時的にレジスタに記録しておいて、

・読み出しの場合はレジスタの内容をそのまま再び書込む

・書き込みの場合はレジスタの内容を書き込むべきデータで上書きしてから書き込む

というようなサイクルを経ます。

書き込み時でも先に読み込みをする必要があるのは、コアの磁化方向を破壊読み出しでいったん揃えてからでないと、前のデータが残ってしまうからです。

コアの磁束が反転するしきい値は形状や種類などによりばらつくと思いますが、少なくとも700~800mAT以上の電流が必要です。

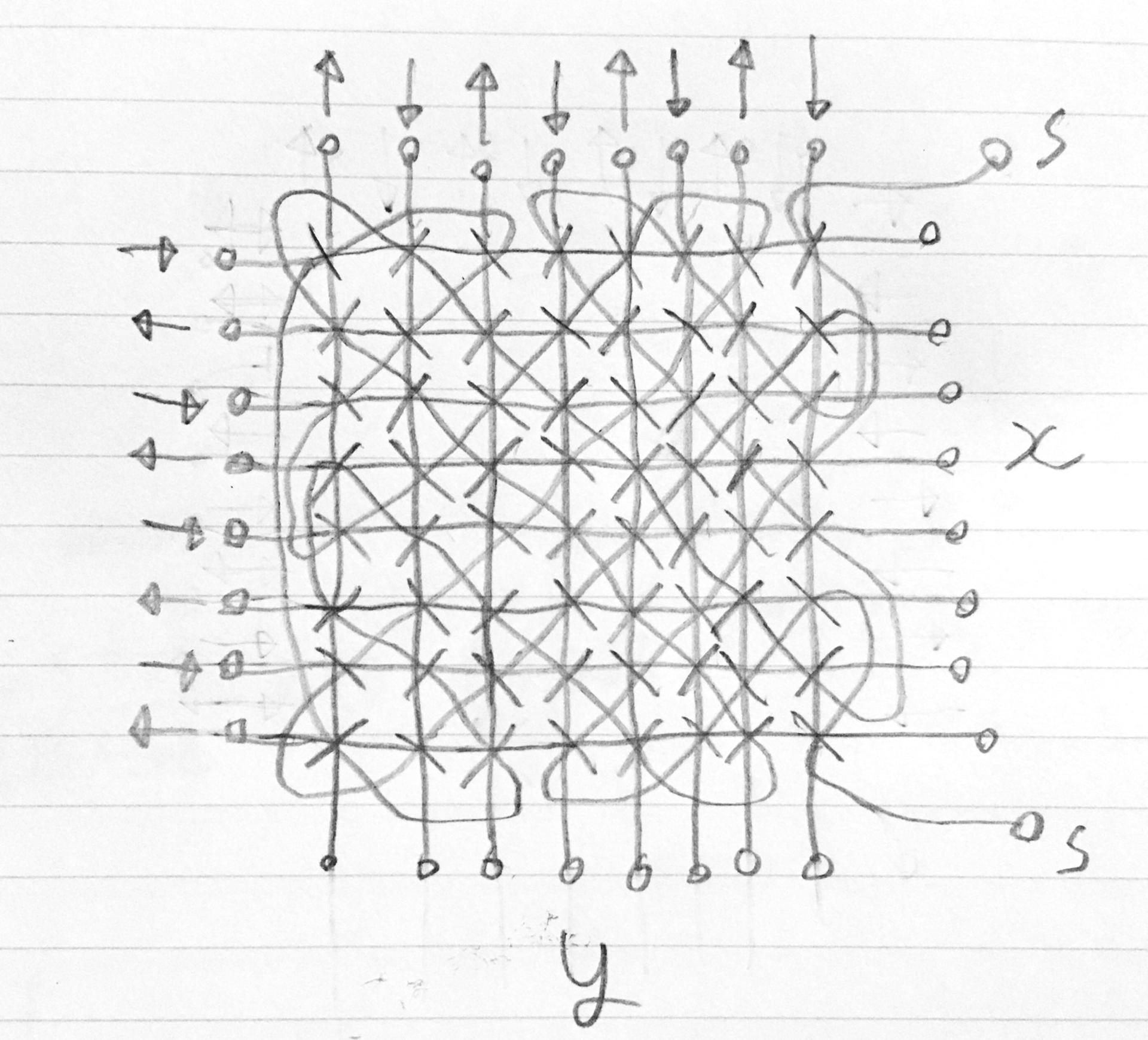

コアマトリクスの配線例イメージ。Sは読み取り線で、x, yは書き込み線。

コアメモリはもともと安価で大容量なメモリとして開発されました。コアひとつひとつにそれぞれ読み書きする回路をつけるのは実用的ではないので、

何らかの方法でたくさんのコアを少ない制御回路で動かしたいわけです。そのため、コアをマトリクス状に配置し、

書き込み線を縦横に碁盤の目のようにしてコア1個あたりに2本通し、それぞれの書き込み線にはしきい値以下の電流を流します。

XとYのそれぞれの書き込み線を1本選択して電流を流し、選択した2つの線が交差するひとつのコアだけがしきい値を超えるようにすることで、

N個のコアを 2√N 本の線で駆動できるようになります。たとえば、256個のコアを32本の線で駆動できるようになります。

また、読み取り線は全てのコアに巡らせて1本だけで済ませることができます。

このように1枚の基板にたくさんのコアをマトリクス状に配置したものをコアマトリクスまたはメモリプレーンと呼び、

コアマトリクスを積層して集積密度をさらに上げたものをコアメモリスタックといいます。

一般に、ひとつのアドレスに格納されているデータの長さを増やすとき、コアマトリクス1枚を1ビットとし、

たとえば8ビットなら8枚重ねのコアメモリスタックを作り、書き込み線をそれぞれ全て直列接続することで、

一度に複数のコアを操作できるようになります。しかし、このまま書込みすると選択した全てのコアに同じものを書き込んでしまうので、

書き込み線と同じ電流量ながら逆方向の電流を流す導線をコアマトリクスに設け、マトリクスごとに書き込みを制御できるようにします。

この導線を禁止線(インヒビット線)といい、コアマトリクスをスタックにした際に必要となります。

(書き込み線で一度に操作するコアが1つだけ、つまりコアマトリクスを1枚だけ使う場合は使用しません)

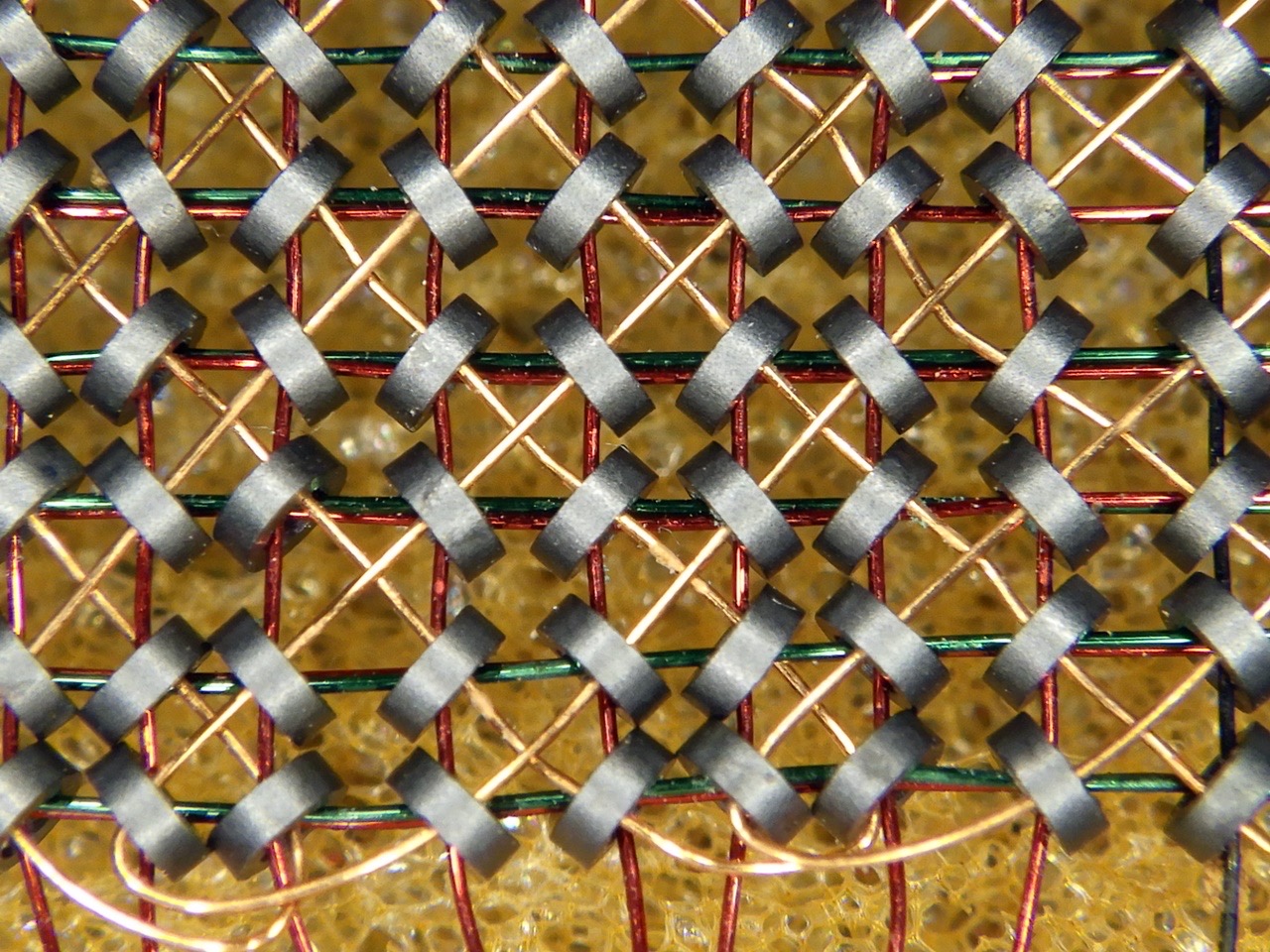

(写真提供:@706GS) これは実際のコアマトリクスの拡大写真で、

赤色の線は書き込み線、黄色は読み取り線、緑色は禁止線となっている。

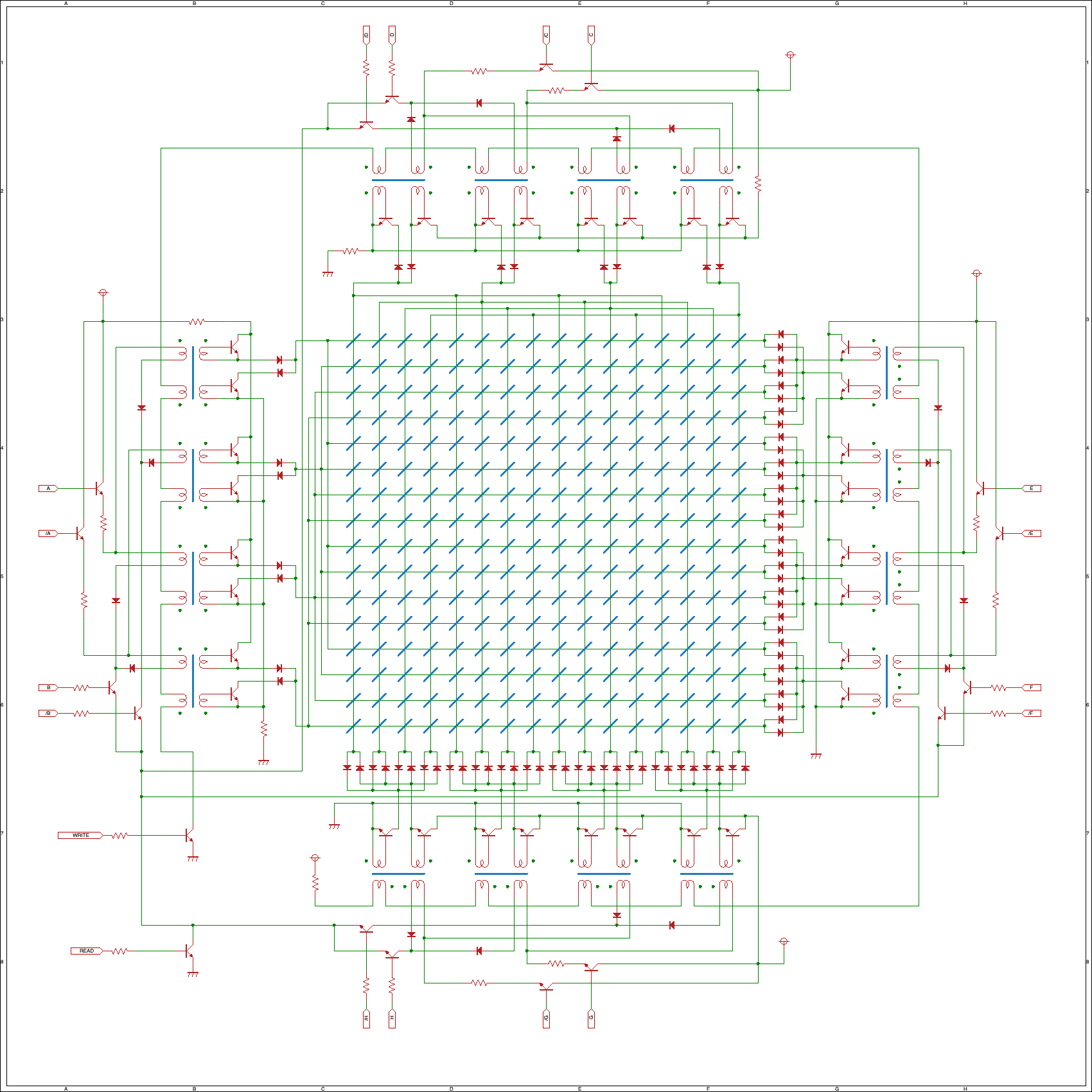

ここで紹介する選択回路は、アポロ誘導コンピュータに使われているものを参考にしています。

コアマトリクスにダイオードマトリクス、ハーフブリッジ回路、

パルストランスをつけて、制御できるようにした回路。

図面を簡単にするため、コアの向きとそれに流す電流の向きは全て同じにしてある。

コアをマトリクスにすることで書き込み線の数は 2√N 個まで削減できるのは先ほど述べた通りですが、

書き込み線を駆動する回路を線それぞれにひとつずつ設けるとハーフブリッジ回路が4√N個(コアが256個なら64個)必要で、さらに巨大な選択回路も必要です。

そこで、書き込み線は一度にひとつしか選択されないことを利用し、コアマトリクスにダイオードマトリクスをつけると、

4√√N 個(コアが256個なら16個)のハーフブリッジ回路で駆動できるようになるうえ、

選択回路も log2√√N ビットの回路を4個作るだけでよくなります。マトリクス一枚あたりのコアが256個なら、2ビットデコーダを4個作るだけです。簡単ですね!

さらに、ハーフブリッジ回路のトランジスタをメモリコアと同じようなヒステリシス特性を持つパルストランスで駆動すると、選択回路と書き込み回路がさらに簡略化できます。

パルストランスには4つの巻線があり、正極性のものと負極性のものがそれぞれ2つずつ巻いてあります。巻線の役割と接続先などは以下の表の通り。

| 役割 | 極性 | 接続先 |

| ストローブ入力 | 正 | 選択回路 |

| リセット入力 | 負 | リセット回路 |

| 出力 | 正 | 出力トランジスタ |

| 出力 | 負 | 出力トランジスタ |

ストローブ入力に接続される選択回路はダイオードマトリクスで構成されていて、外部からのストローブ信号により、選択回路で選択された4つのパルストランスへ同時に電流を流します。

このストローブ信号により正極性側のトランジスタが駆動され、書き込み線に電流が流されます。

全てのパルストランスのリセット入力は直列接続されていて、外部からのリセット信号で同時に電流が流されます。リセット巻線は負極性側のトランジスタを駆動するようにできているものの、

リセット巻線を駆動する前にストローブ信号が来ていなかった場合、ヒステリシス性によって磁束が変化しないためトランジスタは駆動されません。

とどのつまり、リセット信号が入力されたとき、直前に読み込みをしたコアの書き込み線だけに書き込み電流が流れるようになっているのです。

磁気コアメモリに類似したメモリー装置として、コアロープメモリというものがあります。磁気コアメモリはRAMとして動作しますが、コアロープメモリは読み取り専用のROMとして動作します。

コアロープメモリは磁気コアメモリと同じ形状を持つパーマロイなどでできたのコアが使われますが、書き込み線に相当するものは1本だけで、代わりに読み取り線と禁止線がいくつかあります。

そのため、コアのサイズは磁気コアメモリよりも大きいです。

情報を「書き込む」のは、該当するビットの読み取り線を該当するアドレスのコアに通すか通さないかで行います。コアに読み取り線が通っていれば、そのコアを励磁した時に読み取り線にパルスが出ますが、

通さなかった時はパルスは出ないので、それを増幅してレジスタに記憶することで、書き込まれた情報を読み出すことができます。さらに、ひとつのコアにいくつもの読み取り線を通すことで、集積度を上げられます。

アポロ誘導コンピュータでは、コア1個あたり192本の読み取り線が通っていて、コア1個に12ワードのデータを格納していました。

コアロープメモリは、構造上いちど通した読み取り線を変更するのは容易ではないうえ、組み立てに多大な労力と時間を費やすところが欠点です。

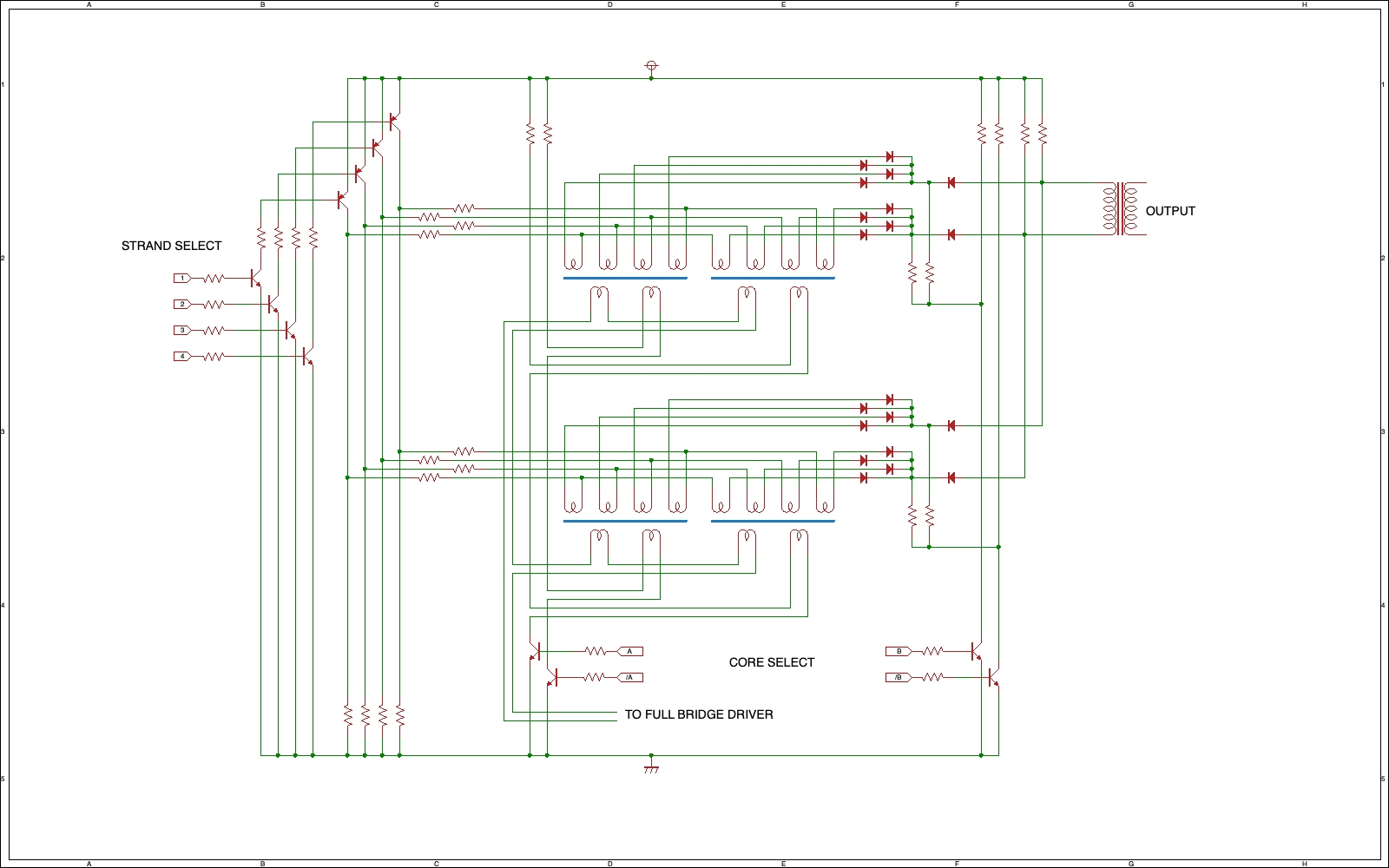

コアロープメモリの回路例。4つのコアそれぞれに4ビットが保存可能で、計16ビットのROMとなっている。

コアロープメモリの読み取り線のことをストランドといいます。

ダイオードスイッチ回路を使うことで、いくつもあるストランドのうちひとつを選択できます。

図の回路では、ストランドを選択するとダイオードが導通し、ストランドにコモンモード電流が流れます。

この状態でストランドに信号電流が現れると平衡が損なわれ、パルストランスにノーマルモード電流が流れます。

このようにして、ひとつのストランドの信号だけが読み取り増幅器に届くようにします。

複数のコアを選択したい場合、禁止線を用いて選択を行います。読み出しをする前に一旦全てのコアを同じ方向に磁化し、

読み出すコア以外の禁止線にそれと同じ方向の電流を流して「禁止」しておきます。この状態で「書き込み線」に禁止線と逆方向の電流を流すと、

「禁止」されていないコアの磁束だけが反転し、ストランドに信号電流が流れます。

コアがたくさんある場合、禁止線を工夫しながら何本も通すことで、2進数アドレスデコード回路を簡素化することが可能です。

参考:Software woven into wire: Core rope and the Apollo Guidance Computer

このページへのコメント

学生のころに実物を見る機会がありました。